### 目次

| [1] 適用範囲                           | 2  |

|------------------------------------|----|

| [2] 概 要                            | 2  |

| [3] ブロック図                          | 2  |

| <br>[4] 外形寸法とマーキング図                | 3  |

| [5]端子説明                            |    |

| [6] 絶対最大定格                         |    |

| [7] 推奨動作条件                         |    |

| [8] 電気的特性                          |    |

| [9] 磁気特性                           |    |

| [10] 測定回路                          |    |

| [11] 極性                            |    |

| [12] タイミングチャート                     |    |

| 12-1. I2Cバス タイミングチャート              |    |

| 12-2. Power OFF and Power ON       |    |

| [13] 測定タイミングダイアグラム                 | 8  |

| 13-1. Normal State                 |    |

| 13-2. Force State                  | 9  |

| 13-3. オフセット調整                      |    |

| 13-3-1. オフセット調整とは                  | 11 |

| 13-3-2. HOSTが保持するパラメータ             | 11 |

| 13-3-3. 手順                         | 11 |

| 13-3-4. Offset registers           | 13 |

| 13-4. Self –test                   | 14 |

| [14] 制御インターフェース                    | 15 |

| 14-1. Power Supplies               | 15 |

| 14-1-1. AVDD                       | 15 |

| 14-1-2. DVDD                       |    |

| 14-1-3. Internal dropout regulator | 15 |

| 14-2. I2C slave interface          |    |

| 14-3. Interrupt signal             |    |

| 14-4. DRDY signal                  |    |

| 14-5. レジスタ                         |    |

| 14-5-1. 出力レジスタ                     |    |

| 14-5-2. 制御レジスタ                     |    |

| [15] コマンド                          |    |

| 15-1. コマンドシーケンス                    |    |

| 15-1-1. リードコマンド                    |    |

| 15-1-2. ライトコマンド                    |    |

| [16] レジスタ                          |    |

| 16-1. レジスタの形式                      |    |

| 16-2. レジスタマップ                      |    |

| 16-3. レジスタマップ詳細                    |    |

| [17] 信 頼 性 試 験 条 件                 |    |

| [18] 半田付けリフロー条件                    |    |

| [19] 注 意 事 項                       | 32 |

### [1] 適用範囲

本仕様書は、愛知製鋼株式会社が、\*\*\*\*に納入する3軸磁気センサ AMI305 に適用します。

#### [2] 概要

AMI305 は 3 方向の磁気を感知するための各々の MI センサーと、そのセンサを動作させるための制御用 IC を小型パッケージに集積化したインテリジェント電子コンパスです。

AMI305の制御用ICは、3個のMIセンサから磁気信号を検出するための専用回路と、各センサの原 点と感度を適当な値に補正を行なうことができる増幅器と、周囲温度を測定できる温度センサと、12bitADコンバータと、I2Cのシリアル出力回路と、定電圧回路と、各回路を制御するロジック回路とを持っています。

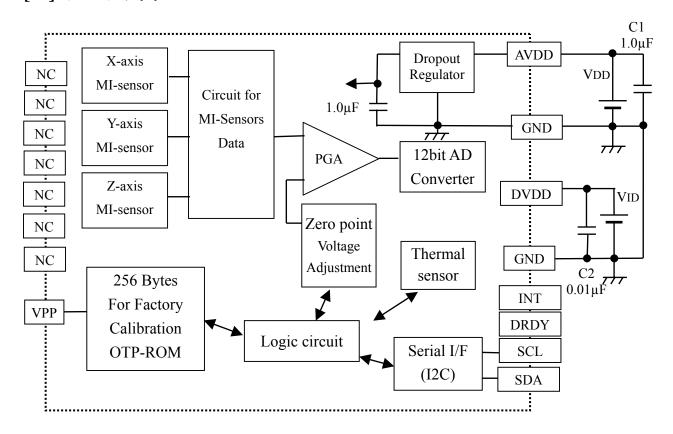

#### [3] ブロック図

#### Note)

制御信号のSCLとSDAには、DVDDとの間にESD保護ダイオードが入っています。SCLとSDAはDVDD+0.3Vより大きな電圧の許容性がありません。

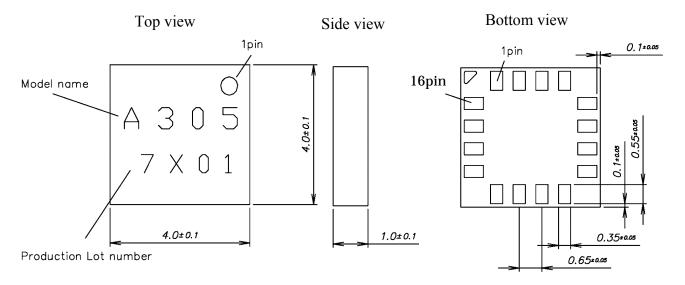

## [4] 外形寸法とマーキング図

## [5]端子説明

| 端子名  | 端子<br>No. | 入出力 | 機能               | 条件              |

|------|-----------|-----|------------------|-----------------|

|      | 110.      |     |                  |                 |

| DVDD | 1         | 電源  | Digital 回路部電源端子  | DVDD-GND の端子近傍に |

| GND  | 2         | 電源  | Digital Ground端子 | 0.01μFのパスコンを実装し |

|      |           |     |                  | てください。          |

| AVDD | 3         | 電源  | Analog 回路部電源端子   | AVDD-GND の端子近傍に |

| GND  | 4         | 電源  | Analog Ground端子  | 1.0μFのパスコンを実装して |

|      |           |     |                  | ください。           |

| NC   | 5-11      | -   | 無接続端子            | _               |

| Vpp  | 12        | -   | 検査用端子            | 無接続で使用してください    |

| INT  | 13        | 出力  | 割り込み出力端子         | _               |

| DRDY | 14        | 出力  | 測定終了を知らせる出力端子    | _               |

| SCL  | 15        | 入出力 | I2C通信用クロック入力端子   | _               |

| SDA  | 16        | 入出力 | I2C通信用データ入出力端子   | _               |

## [6] 絶対最大定格

| 項目   | 記号   | 定格値             | 単位 |

|------|------|-----------------|----|

| 電源電圧 | Vdd  | -0.3 to +5.0    | V  |

|      | Vid  | -0.3 to +4.0    | V  |

| 保存温度 | Tstg | -40 to +125     | °C |

| 入力電圧 | Vin  | -0.3 to VID+0.3 | V  |

### [7] 推奨動作条件

| 項目   | 記号   | Min. | Тур. | Max. | 単位 |

|------|------|------|------|------|----|

| 電源電圧 | Vdd  | 1.70 | 2.50 | 3.60 | V  |

|      | Vid  | 1.70 | 1.80 | VDD  | V  |

| 動作温度 | Topr | -20  |      | +85  | °C |

### [8] 電気的特性

(AVDD=+2.50V 、DVDD=+1.80V 、AVDD - GND に 1.0μFのセラミックコンデンサ)

| 項目                   | 記号    | 条件                                  | Min.        | Тур.   | Max.        | 単位  |

|----------------------|-------|-------------------------------------|-------------|--------|-------------|-----|

| 測定時                  | IDD1  | Output Data Rate = 20SPS,           |             | 0.15   | 1           | mA  |

| 平均動作電流               | IID1  | Normal-Mode                         |             | 0.1    | 2.0         | μΑ  |

| Stand-by 時           | IDD2  | AVDD= +2.4V to 2.9V                 |             | 7      | 10          | μΑ  |

| 動作電流                 | IID2  |                                     |             | 0.1    | 2.0         | μΑ  |

| OFF-mode             | IDD3  |                                     |             |        | 1           | μΑ  |

| Leak 電流              | IID3  |                                     |             |        | 1           | μΑ  |

| ADC 分解能              |       |                                     |             | 12     |             | bit |

| I2C 動作周波数            | fscl  |                                     | 0           |        | 400         | kHz |

| スタートコンディション<br>セット時間 | tsta  |                                     | 0.6         |        |             | μs  |

| ハイレベル入力電圧            | Vih   |                                     | 70%         |        |             | V   |

| ハイレベル八万电圧            | VIII  |                                     | DVDD        |        |             | v   |

| ローレベル入力電圧            | VIL   |                                     |             |        | 30%         | V   |

|                      |       |                                     |             |        | DVDD        |     |

| ハイレベル出力電圧            | Voh   |                                     | 80%<br>DVDD |        |             | V   |

| ローレベル出力電圧            | Vol   | IOL = +3mA                          | BVBB        |        | 20%<br>DVDD | V   |

| I2C アドレス             |       |                                     | 1           | Fh/rea |             |     |

|                      |       |                                     | 1Eh/write   |        |             |     |

| Turn on time 1       | tON1  | from Off -mode to Stand-by          |             | 200    | 250         | μs  |

| Turn on time 2       | tON2  | from Stand-by –mode to Active–mode  |             |        | 8           | μs  |

| Turn off time 1      | tOFF1 | from Active -mode to Stand-by -mode |             |        | 30          | μs  |

### [9] 磁気特性

(AVDD=+2.50V 、DVDD=+1.80V 、AVDD - GND に 1.0μFのセラミックコンデンサ)

| 項目                       | 記号     | 条件                                                      | Min. | Тур.  | Max.  | 単位              |

|--------------------------|--------|---------------------------------------------------------|------|-------|-------|-----------------|

| 動作範囲(*1)                 | Rm     | Ta= +25 °C                                              |      | ± 6.0 |       | gauss           |

| 測定可能範囲<br>(*2)           | Ra     | 出力が飽和しないように<br>XOFFSET, YOFFSET, ZOFFSETで<br>オフセットを調整する |      | ± 12  |       | gauss           |

| 直線性                      | Lin    | $Rm = \pm 1.5 gauss$ , $Ta = +25$ °C                    |      | 0.5   | 2     | %FS             |

| 無磁場での                    |        | Ta= +25 °C                                              |      | 0     |       | LSB             |

| 出力                       | Vofs   | 温度による変化量<br>(Ta=+25°C 基準、Ta=0~+60)                      | -3   |       | +3    | milligauss<br>/ |

|                          |        | Ta= +25 °C                                              |      | 300   |       | LSB/gauss       |

| 磁気感度                     | deltaV | 温度による変化率<br>(Ta=+25°C 基準、Ta=0~+60)                      | -7   |       | +5    | %               |

| 方位分解能                    |        | Ta= +25 °C , Rm=±0.3gauss の 水<br>平磁場                    |      | ± 0.9 |       | degree          |

| 方位正確さ                    |        | $Ta= +25$ °C, $Rm= \pm 0.3$ gauss の 水                   |      | . 0.6 | . 1.0 | 1               |

| (*3) (*4)                |        | 平磁場                                                     |      | ± 0.6 | ± 1.0 | degree          |

| ADC                      | Fr     | Ta= +25 °C                                              |      |       | 1000  | SPS             |

| スルーレート                   | ГІ     |                                                         |      |       |       | _               |

| Maximum<br>Exposed Field |        | センサの動作に影響を与えない磁場                                        |      |       | 10000 | gauss           |

- \*1: 動作範囲: 測定領域があらかじめセットされています。

- \*2: 測定可能範囲: 適切なオフセットに調整することで総合的に測定できる範囲です。

- \*3: PCB に製品を取り付けた後に、再校正します。

- \*4: 軸干渉は"Axis interference" レジスタ を用いて補正されています。

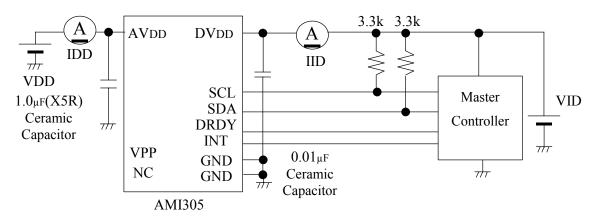

### [10] 測定回路

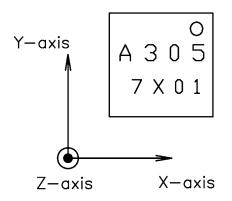

### [11] 極性

矢印の方向は北を向けたときに+となる方向です。

### [12] タイミングチャート

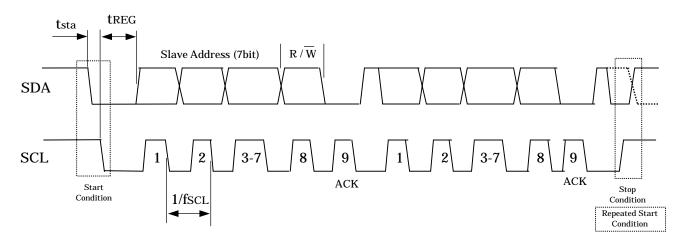

#### 12-1. I2C バス タイミングチャート

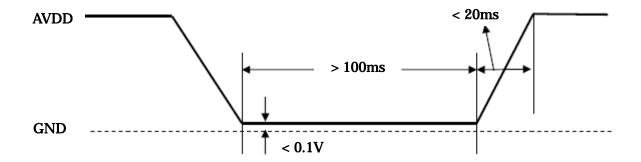

#### 12-2. Power OFF and Power ON

安定した起動を実現するため、Host は 下図 の制御をしなければなりません。.

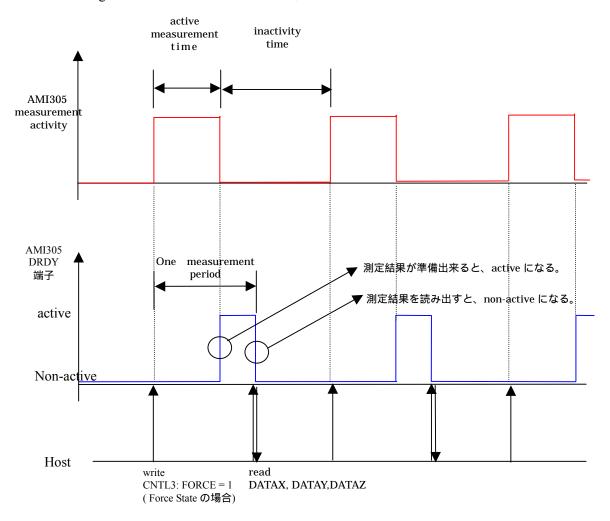

## [13] 測定タイミングダイアグラム

測定モードには、下記の2通りがある。

| Normal State | AMI305 は、指定された周期 (10SPS or 20SPS)で周期測定を行う。 |

|--------------|--------------------------------------------|

| Force State  | ホストからの測定要求にて、AMI305 は測定を行う。                |

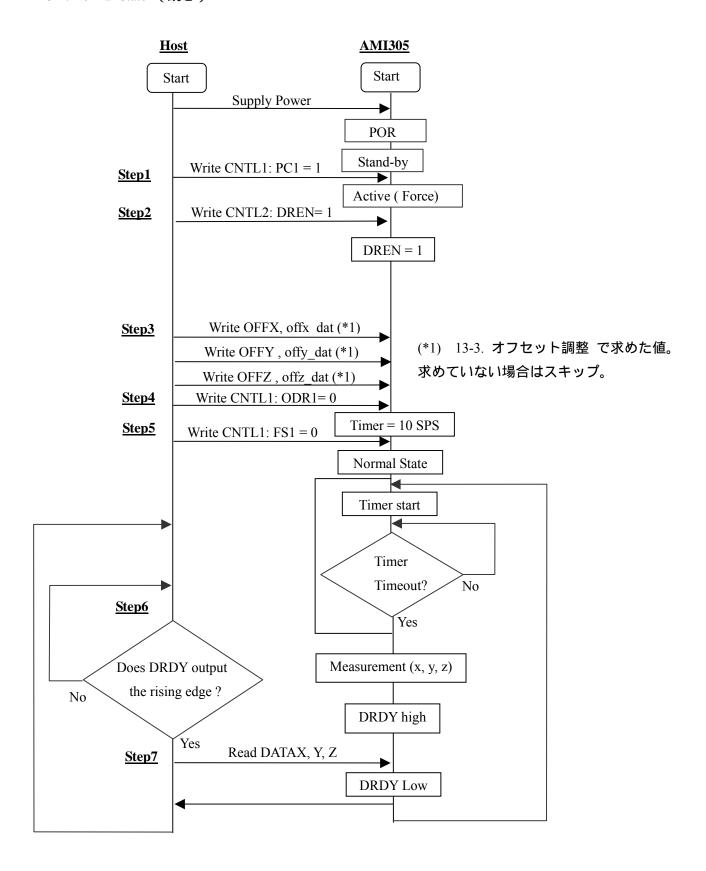

#### 13-1. Normal State

### Normal State sequence

| Step1 | AMI305 Active (Force State)       |

|-------|-----------------------------------|

| Step2 | Set DRDY ready function enable    |

| Step3 | Set offx dat, offy dat, offz dat  |

| Step4 | Set Output Data rate              |

| Step5 | Set Normal state                  |

| Step6 | Does DRDY output the rising edge? |

| Step7 | Read DATAX, DATAY, DATAZ          |

13-1. Normal State (続き)

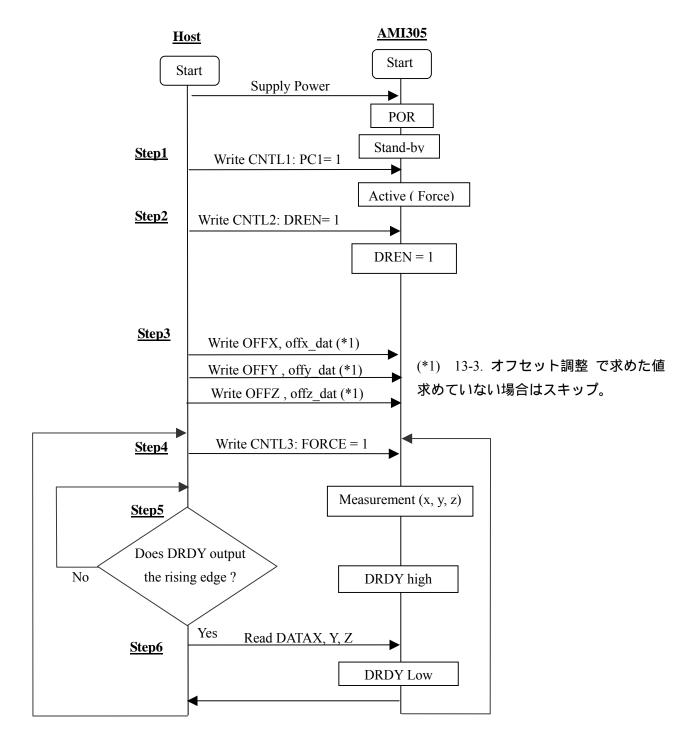

#### 13-2. Force State

Force State sequence

| Step1 | AMI305 Active (Force State)       |

|-------|-----------------------------------|

| Step2 | Set DRDY ready function enable    |

| Step3 | Set offx_dat, offy_dat, offz_dat  |

| Step4 | Measurement Request               |

| Step5 | Does DRDY output the rising edge? |

| Step6 | Read DATAX, DATAY, DATAZ          |

| Step7 | Next Step5                        |

#### 13-3. オフセット調整

#### 13-3-1. オフセット調整とは

電気的に動作点を変更する事で、実装後の磁気環境下で出力値を 0 付近にする事である。

#### 13-3-2. HOST が保持するパラメータ

ホストは、下記のパラメータを下記の 11-3-3. 手順で求めた後、メモリに保存し、AMI305 の電源投入後に設定する必要がある。

| No | Parameter | 内容            |

|----|-----------|---------------|

| 1  | offx_dat  | X 軸のオフセットの調整値 |

| 2  | offy_dat  | Υ 軸のオフセットの調整値 |

| 3  | offz_dat  | Z軸のオフセットの調整値  |

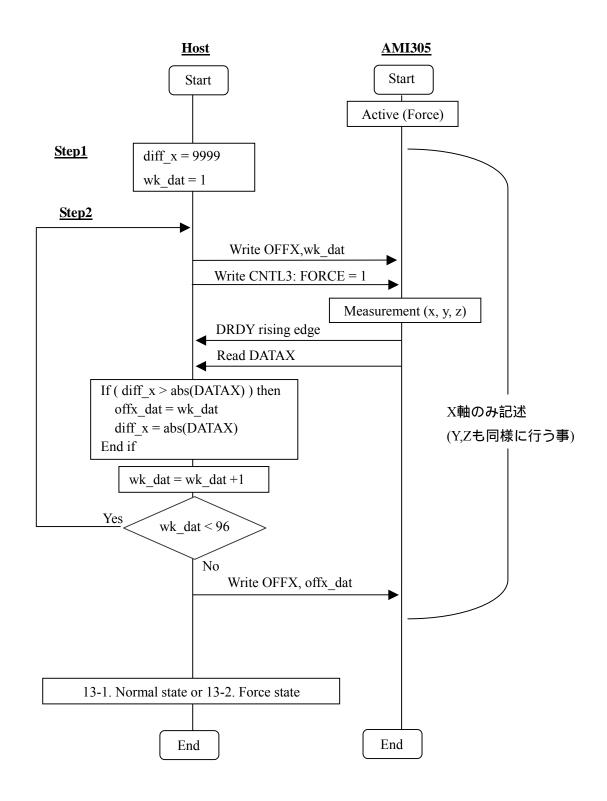

#### 13-3-3. 手順

オフセット調整の手順を下記に示す。

#### 手順

| Step1 | 設定値の初期化。                      |

|-------|-------------------------------|

| Step2 | それぞれの OFFX の組み合わせを見つけることによって、 |

|       | offx_dat を入手します。              |

13-3-3. 手順(続き)

13-3-4. Offset registers

Offset レジスタには fine があります。

下表は Offset X レジスタ の構造を示します。

|      | address | 7bit     | 6bit | 5bit | 4bit  | 3bit | 2bit | 1bit | 0bit |

|------|---------|----------|------|------|-------|------|------|------|------|

| OFFX | 0x6C    | Reserved |      |      |       | fine |      |      |      |

|      |         | X        | X    | X    | X     | X    | X    | X    | X    |

|      | 0x6D    |          |      |      | Reser | ved  |      |      |      |

Offset Y、Offset Z レジスタ も同じ構造です。

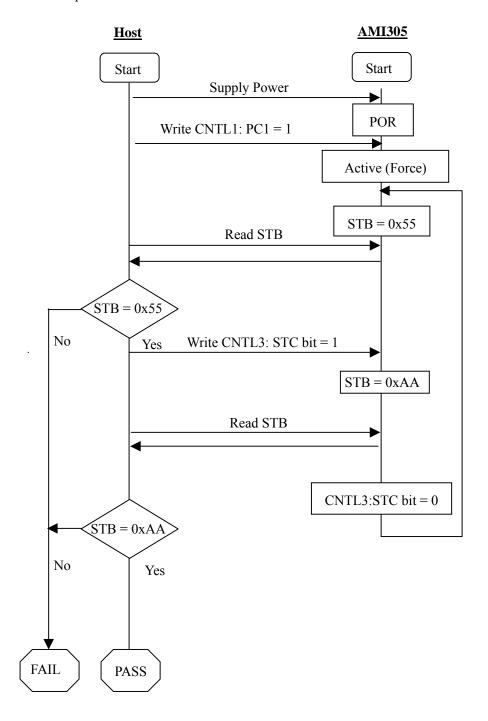

13-4. Self –test

Self-test は電気的な機能性を確認するために使用されます。 Self-test は単純な機能で、この応答は既知の期待値と比較されます。

Self -test sequence

## [14] 制御インターフェース

14-1. Power Supplies

14-1-1. AVDD

AVDD は電源を供給する端子です。AMI305 はこの端子から供給される電流で動作します。

14-1-2. DVDD

DVDD はデジタル入出力の基準電圧の端子です。

14-1-3. Internal dropout regulator

AMI305 は AVDD からの電源を安定化するために定電圧 regulator を内蔵しています。

#### 14-2. I2C slave interface

I2C インターフェースを下記に示す。

| 端子  | 内容        |

|-----|-----------|

| SCL | I2C Clock |

| SDA | I2C Data  |

| Master/ slave | Slave only                                   |

|---------------|----------------------------------------------|

| Address       | アドレスは7ビット構成である。                              |

|               | アドレスは 0001111b ( 0x1F/read, 0x1E/wirte ) です。 |

| 転送速度          | Fast mode 400kHz                             |

#### 14-3. Interrupt signal

本 IC に入力される MI センサからの信号レベルを監視するものあり、全測定モード共通の機能です。規定レベルを超えた信号が入力されると、下記のシーケンスを行う。

INS1 の該当軸のビットを"1"をライト。

各軸の INS1 をまとめて、3 軸の OR 信号とし STA1:INT をライト STA1:INT(='high')を、INT 端子より出力。

解除は、INL をリードすることで行われ、これにより各軸の INS1 及び STA1:INT (INT 端子)がクリアされます。また、どの軸で発生したかは、INS1 で判別できます。

#### 関係するレジスタは下記の通り。

| レジスタ                | 設定内容                               |  |  |  |  |  |

|---------------------|------------------------------------|--|--|--|--|--|

| THR1                | 規定レベル                              |  |  |  |  |  |

| STA1:INT            | interrupt 発生の有無                    |  |  |  |  |  |

| INS1:PXSI,PYSI,PZSI | 各軸の interrupt 発生の有無                |  |  |  |  |  |

| NXSI,NYSI,NZSI      |                                    |  |  |  |  |  |

| INL                 | Interrupt クリア                      |  |  |  |  |  |

| CNTL2 : IEN         | interrupt function Enable/ disable |  |  |  |  |  |

| INC1: XIEN          | X interrupt Enable/ disable        |  |  |  |  |  |

| INC1: YIEN          | Y interrupt Enable/ disable        |  |  |  |  |  |

| INC1: ZIEN          | Z interrupt Enable/ disable        |  |  |  |  |  |

| INC1: IEA           | INT 端子 Active level Low / High     |  |  |  |  |  |

| INC1: IEL           | signal latched/one pulse           |  |  |  |  |  |

#### 14-4. DRDY signal

DRDY signal のシーケンスを下記に示す。

inactivity time 中に測定結果が読み出されなかった場合、STAT1:DOR をセットします。

関係するレジスタは下記の通り。

| レジスタ       | 内容                              |

|------------|---------------------------------|

| CNTL2:DREN | DRDY 端子 Enable/ disable         |

| CNTL2:DRP  | DRDY 端子 Active Level Low / High |

| STA1:DRDY  | DRDY 端子の状態                      |

| STA1:DOR   | 出力データのオーバーラン                    |

### 14-5. レジスタ

#### 14-5-1. 出力レジスタ

磁気の測定結果及び状態を出力する。

#### 磁気の測定結果

| DATAX | X channel 測定結果 |

|-------|----------------|

| DATAY | Y channel 測定結果 |

| DATAZ | Z channel 測定結果 |

#### Status register(s)

| STAT1 | Status |

|-------|--------|

|-------|--------|

### 14-5-2. 制御レジスタ

#### 本 IC を制御するレジスタは下記の通りである。

#### Control register(s)

| Power modes        | CNTL1        |

|--------------------|--------------|

| Functional state   | CNTL2        |

| Interrupt controls | INC1 / ITHR1 |

#### Measure register(s)

| Measurement mode | CNTL1/ CNTL3 |

|------------------|--------------|

| Preset time      | PRET         |

| temperature      | ТЕМР         |

### [15] コマンド

#### 15-1. コマンドシーケンス

コマンドは、リードコマンドとライトコマンドの2パタンです。 リードコマンドは、レジスタの読み込み及び出力値の呼び出し時に使用する。 ライトコマンドは、レジスタの設定時に使用する。

コマンドシーケンスを下記に示す。

#### 15-1-1. リードコマンド

| Master | S | SAD+   |   | RAD |   | Sr | SAD+   |   |      | Α |      | Α |   | N | P |

|--------|---|--------|---|-----|---|----|--------|---|------|---|------|---|---|---|---|

|        |   | W (*1) |   |     |   |    | R (*1) |   |      |   |      |   |   |   |   |

| Slave  |   |        | A |     | A |    |        | A | RDA1 |   | RDA2 |   | • |   |   |

| Term | Definition        | Term    | Definition            |

|------|-------------------|---------|-----------------------|

| S    | Start Condition   | SAD + W | slave address + write |

|      |                   |         | (0x1E)                |

| Sr   | Restart Condition | SAD + R | slave address + read  |

|      |                   |         | (0x1F)                |

| A    | ACK (SDA_Low)     | RAD     | 読み込みアドレス              |

|      | _                 |         | (register)            |

| N    | NACK (SDA_High)   | RDA1    | 読み込みデータ1              |

| P    | Stop Condition    | RDA2    | 読み込みデータ2              |

(\*1) 7 6 5 4 3 2 1 0 SAD W/R

#### 15-1-2. ライトコマンド

| Master | S | SAD+W (*1) |   | WAD |   | WDA1 |   | WDA2 |   |   | P |

|--------|---|------------|---|-----|---|------|---|------|---|---|---|

| Slave  |   |            | Α |     | Α |      | Α |      | A | Α |   |

| Term | Definition      | Term    | Definition            |

|------|-----------------|---------|-----------------------|

| S    | Start Condition | SAD + W | slave address + write |

|      |                 |         | (0x1E)                |

| A    | ACK (SDA_Low)   | WAD     | 書き込みアドレス              |

|      |                 |         | (register)            |

| N    | NACK (SDA_High) | WDA1    | 書き込みデータ1              |

| P    | Stop Condition  | WDA2    | 書き込みデータ2              |

(\*1) 7 6 5 4 3 2 1 0 SAD W/R

### [16] レジスタ

#### 16-1. レジスタの形式

レジスタの形式を下記に纏める。

| Type  | Items               | Comments                 |

|-------|---------------------|--------------------------|

| TYPE1 | 制御及び状態              | 符号なし1バイト(unsigned char)。 |

| TYPE2 | 温度                  | 2の補数の符号あり1バイト。           |

|       |                     | -128d = 0x80             |

|       |                     | 0d = 0                   |

|       |                     | 127d = 0x7F              |

| TYPE3 | 磁気などの出力             | 2の補数の符号あり2バイト。           |

|       |                     | -2048d = 0xF800          |

|       |                     | 0d = 0x000               |

|       |                     | 2047d = 0x07FF           |

|       |                     | 格納形式は、Little Endian である。 |

| TYPE4 | Interrupt threshold | unsigned 2 byte.         |

|       |                     | 0d = 0x0000              |

|       |                     | 2047d = 0x07FF           |

|       |                     | 格納形式は、Little Endian である。 |

16-2. レジスタマップ

レジスタを、下記に示す。各アドレスのデータ幅は8ビットです。

| Reg.Name | Address   | Type  | R/W | Set Contents        | Remark |

|----------|-----------|-------|-----|---------------------|--------|

| Not used | 0x00-0x0B | -     | -   | -                   | -      |

| STB      | 0x0C      | TYPE1 | -   | Self-test response  | -      |

| INFO     | 0x0D/0x0E | TYPE3 | R   | More Info           | -      |

| WIA      | 0x0F      | TYPE1 | R   | Who I am            | -      |

| DATAX    | 0x10/0x11 | TYPE3 | R   | X Output value      | -      |

| DATAY    | 0x12/0x13 | TYPE3 | R   | Y Output value      | -      |

| DATAZ    | 0x14/0x15 | TYPE3 | R   | Z Output value      | -      |

| INS1     | 0x16      | TYPE1 | R   | Interrupt source1   | -      |

| Not used | 0x17      | 1     | -   | -                   | -      |

| STAT1    | 0x18      | TYPE1 | R   | Status1             | -      |

| Not used | 0x19      | -     | -   |                     | -      |

| INL      | 0x1A      | TYPE1 | R   | Interrupt release   | -      |

| CNTL1    | 0x1B      | TYPE1 | R/W | Control setting 1   | -      |

| CNTL2    | 0x1C      | TYPE1 | R/W | Control setting 2   | -      |

| CNTL3    | 0x1D      | TYPE1 | R/W | Control setting 3   | -      |

| INC1     | 0x1E      | TYPE1 | R/W | Interrupt Control1  | -      |

| Not used | 0x1F      | ı     | -   | -                   | -      |

| ITHR1    | 0x26/0x27 | TYPE4 | R/W | Interrupt threshold | -      |

| -        | 0x28-0x2F | 1     | -   | Reserved            | -      |

| PRET     | 0x30      | TYPE1 | R/W | Preset time         | -      |

| -        | 0x46-0x5F | -     | -   | Reserved            | -      |

| TEMP     | 0x60/0x61 | TYPE4 | R   | Temperature value   | -      |

| OFFX     | 0x6C/0x6D | TYPE4 | R/W | Offset X value      | -      |

| OFFY     | 0x72/0x73 | TYPE4 | R/W | Offset Y value      | -      |

| OFFZ     | 0x78/0x79 | TYPE4 | R/W | Offset Z value      | -      |

| -        | 0x7A-0x95 | -     | -   | Reserved            |        |

| VER      | 0xE8/0xE9 | TYPE4 | R   | Firmware version    | -      |

| SN       | 0xEA/0xEB | TYPE4 | R   | Serial Number       | -      |

Note1) TYPE3 と TYPE4 は 2bytes 単位で通信してください。

#### 16-3. レジスタマップ詳細

"Self-Test Response" Register

Self-Test Response

| Register | Туре     | Main Usage         |

|----------|----------|--------------------|

| STB      | 8bit / R | Self test response |

|     | address | 7bit | 6bit     | 5bit | 4bit              | 3bit | 2bit | 1bit | 0bit |

|-----|---------|------|----------|------|-------------------|------|------|------|------|

| STB | 0x0C    |      | CC/CRTL: |      | B=0xAA<br>CRTL3=0 |      |      |      |      |

<sup>&</sup>quot;Information " Register

#### Information

| Register | Type      | Main Usage |

|----------|-----------|------------|

| INFO     | 16bit / R |            |

|      | address | 7bit | 6bit | 5bit | 4bit | 3bit | 2bit | 1bit | 0bit |

|------|---------|------|------|------|------|------|------|------|------|

| INFO | 0x0D    | X    | X    | X    | X    | X    | X    | X    | X    |

|      | 0x0E    | X    | X    | X    | X    | X    | X    | X    | X    |

<sup>&</sup>quot;Who I Am " Register

#### Who I Am

| Register | Type     | Main Usage |

|----------|----------|------------|

| WIA      | 8bit / R |            |

|     | address | 7bit | 6bit | 5bit | 4bit | 3bit | 2bit | 1bit | 0bit |

|-----|---------|------|------|------|------|------|------|------|------|

| WIA | 0x0F    |      |      |      | 0x   | 47   |      |      |      |

"Output value "Registers

#### X Output value

| Register | Туре      | Main Usage     |

|----------|-----------|----------------|

| DATAX    | 16bit / R | X channel 測定結果 |

|       | address | 7bit | 6bit | 5bit | 4bit | 3bit | 2bit | 1bit | 0bit |

|-------|---------|------|------|------|------|------|------|------|------|

| DATAX | 0x10    | LSB7 | LSB6 | LSB5 | LSB4 | LSB3 | LSB2 | LSB1 | LSB0 |

|       | 0x11    | MSB7 | MSB6 | MSB5 | MSB4 | MSB3 | MSB2 | MSB1 | MSB0 |

#### Y Output value

| Register | Type      | Main Usage     |

|----------|-----------|----------------|

| DATAY    | 16bit / R | Y channel 測定結果 |

|       | address | 7bit | 6bit | 5bit | 4bit | 3bit | 2bit | 1bit | 0bit |

|-------|---------|------|------|------|------|------|------|------|------|

| DATAY | 0x12    | LSB7 | LSB6 | LSB5 | LSB4 | LSB3 | LSB2 | LSB1 | LSB0 |

|       | 0x13    | MSB7 | MSB6 | MSB5 | MSB4 | MSB3 | MSB2 | MSB1 | MSB0 |

### Z Output value

| Register | Type      | Main Usage     |

|----------|-----------|----------------|

| DATAZ    | 16bit / R | Z channel 測定結果 |

|       | address | 7bit | 6bit | 5bit | 4bit | 3bit | 2bit | 1bit | 0bit |

|-------|---------|------|------|------|------|------|------|------|------|

| DATAZ | 0x14    | LSB7 | LSB6 | LSB5 | LSB4 | LSB3 | LSB2 | LSB1 | LSB0 |

|       | 0x15    | MSB7 | MSB6 | MSB5 | MSB4 | MSB3 | MSB2 | MSB1 | MSB0 |

"Interrupt source " Register

Interrupt source

| Register | Type     | Main Usage                    |

|----------|----------|-------------------------------|

| INS1     | 8bit / R | Interrupt 現象が発生した事を各軸単位で保持する。 |

|      | address | 7bit | 6bit | 5bit | 4bit | 3bit | 2bit | 1bit | 0bit |

|------|---------|------|------|------|------|------|------|------|------|

| INS1 | 0x16    | PXSI | PYSI | PZSI | NXSI | NYSI | NZSI | NZSI | -    |

| bit | 名称   | 内容                                    | default |

|-----|------|---------------------------------------|---------|

| 7   | PXSI | +X軸で Interrupt 現象(ITHR1 の閾値を超えた)が発生し  | 0       |

|     |      | た場合、1を書き込む。                           |         |

|     |      | 1に設定された後、INL の読み込みにてクリアされる。           |         |

| 6   | PYSI | +Y 軸で Interrupt 現象(ITHR1 の閾値を超えた)が発生し | 0       |

|     |      | た場合、1を書き込む。                           |         |

|     |      | 1 に設定された後、INL の読み込みにてクリアされる。          |         |

| 5   | PZSI | +Z 軸で Interrupt 現象(ITHR1 の閾値を超えた)が発生し | 0       |

|     |      | た場合、1を書き込む。                           |         |

|     |      | 1 に設定された後、INL の読み込みにてクリアされる。          |         |

| 4   | NXSI | - X軸で Interrupt 現象(ITHR1 の閾値を超えた)が発生し | 0       |

|     |      | た場合、1を書き込む。                           |         |

|     |      | 1に設定された後、INL の読み込みにてクリアされる。           |         |

| 3   | NYSI | -Y 軸で Interrupt 現象(ITHR1 の閾値を超えた)が発生し | 0       |

|     |      | た場合、1を書き込む。                           |         |

|     |      | 1に設定された後、INL の読み込みにてクリアされる。           |         |

| 2   | NZSI | -Z 軸で Interrupt 現象(ITHR1 の閾値を超えた)が発生し | 0       |

|     |      | た場合、1を書き込む。                           |         |

|     |      | 1に設定された後、INL の読み込みにてクリアされる。           |         |

| 1   | MROI | 測定範囲外 (range overflow)                | 0       |

|     |      | (全軸共通)                                |         |

| 0   | -    |                                       | -       |

#### "Status" Register

#### Status1

| Register | Type     | Main Usage      |

|----------|----------|-----------------|

| STA1     | 8bit / R | 端子に出力する情報を格納する。 |

|      | address | 7bit | 6bit | 5bit | 4bit | 3bit | 2bit | 1bit | 0bit |

|------|---------|------|------|------|------|------|------|------|------|

| STA1 | 0x18    | RES  | DRDY | DOR  | INT  | -    | -    | -    | -    |

| bit | 名称   | 内容                                                                                                                                            | default |

|-----|------|-----------------------------------------------------------------------------------------------------------------------------------------------|---------|

| 7   | RES  | Reserved                                                                                                                                      | -       |

| 6   | DRDY | 測定データの準備状態を知らせるビットで、本ビットの出力は DRDY 端子に出力される。 0: 測定データの準備 NG(測定中) 1: 測定データの準備 OK                                                                | 0-      |

| 5   | DOR  | Inactivity time 期間に測定データを読み出されなかった場合に1を設定する。<br>・1に設定された後、読み込み命令でクリアされる。                                                                      | 0       |

| 4   | INT  | Interrupt 発生を知らせるビットで、本ビットの出力は、INT 端子に出力される。 0 = Interrupt 発生していない。 1 = Interrupt 発生 ・どの軸で発生しているかは、INS1 で判別可能である。 ・1 に設定された後、INL の読み込みでクリアされる | 0       |

| 3   | -    | -                                                                                                                                             | -       |

| 2   | -    | -                                                                                                                                             | -       |

| 1   | -    | -                                                                                                                                             | -       |

| 0   | -    | -                                                                                                                                             | -       |

#### "Interrupt release" Register

Interrupt release

| Register | Type   | Main Usage                               |

|----------|--------|------------------------------------------|

| INL      | 8bit R | 本レジスタを読み込む事で INS1 及び STA:INT ビット(INT 端子) |

|          |        | をクリアする。                                  |

|     | address | 7bit | 6bit | 5bit | 4bit | 3bit | 2bit | 1bit | 0bit |

|-----|---------|------|------|------|------|------|------|------|------|

| INL | 0x1A    | -    | -    | -    | -    | -    | -    | -    | -    |

### "Control Setting" Register

Control Setting1

| Control Sc | 7tt1115 1 |                        |

|------------|-----------|------------------------|

| Register   | Type      | Main Usage             |

| CNTL1      | 8bit R/W  | Power モード及び測定モードを設定する。 |

|       | address | 7bit | 6bit | 5bit | 4bit | 3bit  | 2bit | 1bit | 0bit |

|-------|---------|------|------|------|------|-------|------|------|------|

| CNTL1 | 0x1B    | PC1  | PC2  | SC   | ODR1 | ODR2- | ODR3 | FS1  | FS2  |

| bit | 名称   | 内容                    | default |

|-----|------|-----------------------|---------|

| 7   | PC1  | Power Model を設定する。    | 0       |

|     |      | 0 = stand-by          |         |

|     |      | 1 = active            |         |

| 6   | PC2  | Reserved              | 0       |

| 5   | SC   | Reserved              | 0       |

| 4   | ODR1 | Out Data rate1 を設定する。 | 0       |

|     |      | 0 = 10  SPS(10Hz)     |         |

|     |      | 1 = 20  SPS  (20Hz)   |         |

| 3   | ODR2 | Reserved              | 0       |

| 2   | ODR3 | Reserved              | 0       |

| 1   | FS1  | 測定モードを設定する。           | 1       |

|     |      | 0 = Normal            |         |

|     |      | 1 = Force             |         |

| 0   | FS2  | Reserved              | 0       |

Control Setting2

| Register | Type       | Main Usage                                    |

|----------|------------|-----------------------------------------------|

| CNTL2    | 8bit / R/W | Interrupt 端子/DWONE 端子の Enable/Disable の設定をする。 |

|       | address | 7bit | 6bit | 5bit | 4bit | 3bit | 2bit | 1bit | 0bit |

|-------|---------|------|------|------|------|------|------|------|------|

| CNTL2 | 0x1C    | RES  | RES  | RES  | IEN  | DREN | DRP  | RES  | RES  |

| bit | 名称   | 内容                                              | default |

|-----|------|-------------------------------------------------|---------|

| 7   | -    | Reserved                                        | 0       |

| 6   | -    | Reserved                                        | 0       |

| 5   | -    | Reserved                                        | 0       |

| 4   | IEN  | INT 端子のイネーブルを設定する。<br>0 = ディスネーブル<br>1 = イネーブル  | 0       |

| 3   | DREN | DRDY 端子のイネーブルを設定する。<br>0 = ディスネーブル<br>1 = イネーブル | 0       |

| 2   | DRP  | DRDY 端子の Active を設定する。<br>0 = low<br>1 = high   | 1       |

| 1   | -    | Reserved                                        | 0       |

| 0   | -    | Reserved                                        | 0       |

Control Setting3

| [ | Register | Type       | Main Usage    |

|---|----------|------------|---------------|

|   | CNTL3    | 8bit / R/W | 制御パラメータを指定する。 |

|       | address | 7bit | 6bit  | 5bit | 4bit | 3bit | 2bit | 1bit | 0bit |

|-------|---------|------|-------|------|------|------|------|------|------|

| CNTL3 | 0x1D    | SRST | FORCE | RES  | -    | -    | -    | -    | -    |

| bit | ,名称   | 内容                                | default |

|-----|-------|-----------------------------------|---------|

| 7   | SRST  | ソフトリセットを実施する。POR と同じ手順で実施す        | 0       |

|     |       | る。                                |         |

|     |       | 0= 何もしない。                         |         |

|     |       | 1= ソフトリセット(POR と同じ手順)を実施開始する。     |         |

| 6   | FORCE | Force モードにおける測定開始信号(Force trg)を発生 | 0       |

|     |       | させる。                              |         |

|     |       | 0 = 何もしない。                        |         |

|     |       | 1 = ライト後、すぐに Force TRG を発生し、測定を   |         |

|     |       | 開始する。                             |         |

|     |       | (CNT1:FS1=1 の時のみ有効)               |         |

| 5   | -     | Reserved                          | 0       |

| 4   | -     | Reserved                          | 0       |

| 3   | -     | Reserved                          | 0       |

| 2   | -     | Reserved                          | 0       |

| 1   | -     | Reserved                          | 0       |

| 0   | -     | Reserved                          | 0       |

"Interrupt control" Register

Interrupt control 1

| Register | Type       | Main Usage              |

|----------|------------|-------------------------|

| INC1     | 8bit / R/W | Interrupt 制御パラメータを指定する。 |

|      | address | 7bit | 6bit | 5bit | 4bit | 3bit | 2bit | 1bit | 0bit |

|------|---------|------|------|------|------|------|------|------|------|

| INC1 | 0x1E    | XIEN | YIEN | ZEN  | -    | IEA  | IEL  | -    | -    |

| bit | ,名称  | 内容                         | default |

|-----|------|----------------------------|---------|

| 7   | XIEN | X 軸 Interrupt のイネーブルを設定する。 | 1       |

|     |      | 0 = Disable                |         |

|     |      | 1 = Enable                 |         |

| 6   | YIEN | Y 軸 Interrupt のイネーブルを設定する。 | 1       |

|     |      | 0 = Disable                |         |

|     |      | 1 = Enable                 |         |

| 5   | ZEN  | Z軸 Interrupt のイネーブルを設定する。  | 1       |

|     |      | 0 = Disable                |         |

|     |      | 1 = Enable                 |         |

| 4   | -    | -                          | 0       |

| 3   | IEA  | interrupt active を設定する。    | 1       |

|     |      | 0 = low                    |         |

|     |      | 1 = high                   |         |

| 2   | IEL  | interrupt signal を設定する。    | 0       |

|     |      | 0 = latched                |         |

|     |      | 1 = one pulse(0.05ms)      |         |

| 1   |      | -                          | 0       |

| 0   |      | -                          | -       |

#### "Interrupt threshold" register

Interrupt threshold を設定する。データサイズは2バイトである。設定値は下記の通りある。

#### 3 軸とも、Interrupt threshold を使う。

Interrupt threshold1

| Interrupt th | interrupt uneshold |                            |  |  |  |  |  |  |  |  |

|--------------|--------------------|----------------------------|--|--|--|--|--|--|--|--|

| Register     | Type               | Main Usage                 |  |  |  |  |  |  |  |  |

| ITHR1        | 16bit / R/W        | Interrupt threshold を設定する。 |  |  |  |  |  |  |  |  |

|       | address | 7bit | 6bit | 5bit | 4bit | 3bit | 2bit | 1bit | 0bit |

|-------|---------|------|------|------|------|------|------|------|------|

| ITHR1 | 0x26    | LSB7 | LSB6 | LSB5 | LSB4 | LSB3 | LSB2 | LSB1 | LSB0 |

|       | 0x27    | MSB7 | MSB6 | MSB5 | MSB4 | MSB3 | MSB2 | MSB1 | MSB0 |

#### "Preset Time" register

Preset Time

| Register | Type       | Main Usage  |

|----------|------------|-------------|

| PRET     | 8bit / R/W | 測定前のプリセット時間 |

|          |            |             |

|      | address | 7bit | 6bit | 5bit | 4bit | 3bit | 2bit | 1bit | 0bit |

|------|---------|------|------|------|------|------|------|------|------|

| PRET | 0x30    | -    | -    | -    | -    | PS3  | PS2  | PS1  | PS0  |

| bit | Name | Content | default |

|-----|------|---------|---------|

| 7   | -    | -       | 0       |

| 6   | -    | -       | 0       |

| 5   | -    | -       | 0       |

| 4   | -    | -       | 0       |

| 3   | PS3  |         | 0       |

| 2   | PS2  |         | 0       |

| 1   | PS1  |         | 0       |

| 0   | PS0  |         | 0       |

<sup>&</sup>quot;Temperature sensor output value" Register

Temperature sensor output value

| Register | Type      | Main Usage       |

|----------|-----------|------------------|

| TEMP     | 16bit / R | Temperature code |

|      | address | 7bit | 6bit | 5bit | 4bit | 3bit | 2bit | 1bit | 0bit |

|------|---------|------|------|------|------|------|------|------|------|

| TEMP | 0x60    | LSB7 | LSB6 | LSB5 | LSB4 | LSB3 | LSB2 | LSB1 | LSB0 |

|      | 0x61    | MSB7 | MSB6 | MSB5 | MSB4 | MSB3 | MSB2 | MSB1 | MSB0 |

"Offset" registers

電気的動作点を設定する。データサイズは2バイトである。初期値は個体毎に異なる。設定値は下記の通りである。

#### Offset X

| Register | Type        | Main Usage       |

|----------|-------------|------------------|

| OFFX     | 16bit / R/W | X-axis offset 調整 |

|      | address | 7bit     | 6bit | 5bit | 4bit  | 3bit | 2bit | 1bit | 0bit |

|------|---------|----------|------|------|-------|------|------|------|------|

| OFFX | 0x6C    | Reserved | X    | X    | X     | X    | X    | X    | X    |

|      | 0x6D    |          |      |      | Reser | ved  |      |      |      |

#### Offset Y

| 211501   |             |                  |

|----------|-------------|------------------|

| Register | Type        | Main Usage       |

| OFFY     | 16bit / R/W | Y-axis offset 調整 |

|      | address | 7bit     | 6bit | 5b | 4bit  | 3bit | 2bit | 1bit | 0bit |

|------|---------|----------|------|----|-------|------|------|------|------|

| OFFY | 0x72    | Reserved | X    | X  | X     | X    | X    | X    | X    |

|      | 0x73    |          |      |    | Reser | ved  |      |      |      |

#### Offset Z

| Register | Type        | Main Usage       |

|----------|-------------|------------------|

| OFFZ     | 16bit / R/W | Z-axis offset 調整 |

|      | address | 7bit     | 6bit | 5bit | 4bit  | 3bit | 2bit | 1bit | 0bit |

|------|---------|----------|------|------|-------|------|------|------|------|

| OFFZ | 0x78    | Reserved | X    | X    | X     | X    | X    | X    | X    |

|      | 0x79    |          |      |      | Reser | ved  |      |      |      |

<sup>&</sup>quot;Firmware version" Register

| Register | Type      | Main Usage       |

|----------|-----------|------------------|

| VER      | 16bit / R | Firmware version |

|     | address | 7bit | 6bit             | 5bit | 4bit | 3bit | 2bit | 1 bit | 0bit |

|-----|---------|------|------------------|------|------|------|------|-------|------|

| VER | 0xE8    | RES  | Firmware version |      |      |      |      |       |      |

|     | 0xE9    | RES  | RES              | RES  | RES  | RES  | RES  | RES   | RES  |

<sup>&</sup>quot;Serial Number" Register

| Register | Туре      | Main Usage    |

|----------|-----------|---------------|

| SN       | 16bit / R | Serial Number |

|    | address | 7bit | 6bit | 5bit | 4bit | 3bit | 2bit | 1bit | 0bit |

|----|---------|------|------|------|------|------|------|------|------|

| SN | 0xEA    | LSB7 | LSB6 | LSB5 | LSB4 | LSB3 | LSB2 | LSB1 | LSB0 |

|    | 0xEB    | MSB7 | MSB6 | MSB5 | MSB4 | MSB3 | MSB2 | MSB1 | MSB0 |

### [17]信頼性試験条件

| No. | 試験項目                 | 試験条件<br>[EIAJ ED-4701 準拠]                   | *1.<br>前処理 | 試験<br>時間   | n(C=0)<br>[LTPD] | 判定<br>基準                                                                 |

|-----|----------------------|---------------------------------------------|------------|------------|------------------|--------------------------------------------------------------------------|

| 1   | 高温保存                 | Ta=+125°C                                   | 無          | 500 hours  | 22[10%]          |                                                                          |

| 2   | 低温保存                 | Ta= -40°C                                   | 無          | 500 hours  | 22[10%]          |                                                                          |

| 3   | 高温高湿保存               | Ta=+85°C, RH= 85%                           | 1)+2)      | 500 hours  | 22[10%]          |                                                                          |

| 4   | 高温バイアス               | Ta=+125°C, VDD=+3.6V                        | 無          | 500 hours  | 22[10%]          |                                                                          |

| 5   | 高温高湿バイアス             | Ta=+85°C, RH= 85%,<br>VDD=+3.6V             | 1)+2)      | 500 hours  | 22[10%]          | 感度変化率が                                                                   |

| 6   | 温度サイクル               | -40°C ↔ +125°C<br>(30min - 5min - 30min)    | 1)+2)      | 100 cycles | 22[10%]          |                                                                          |

| 7   | 熱衝撃                  | -40°C ↔ +125°C<br>(5min - 10s - 5min)       | 1)+2)      | 100 cycles | 22[10%]          |                                                                          |

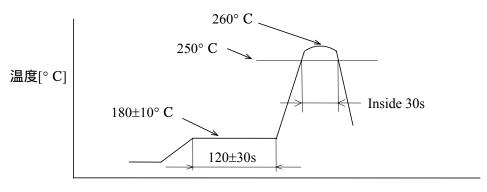

| 8   | はんだ耐熱                | 赤外線リフロー (下図参照:高温<br>リフロー対応可ピーク+260 以<br>下)  | 1)         | 3 times    | 22[10%]          |                                                                          |

| 9   | 静電気耐量                | C= 100pF, R= 1.5k ohm, ±2kV (Min.)          | 無          | 3 times    | 22[10%]          |                                                                          |

| 10  | CDM 耐量               | ± 500V                                      | 無          | 1 time     | 22[10%]          |                                                                          |

| 11  | 基板曲げ                 | Support Span 90mm, Flex 3mm,                | 無          | 1 time     | 22[10%]          |                                                                          |

|     |                      | 5 ± 1 second hold                           |            |            |                  |                                                                          |

| 12  | はんだ付け性               | Ta=+235°C                                   | 3)         | 3 seconds  | 22[10%]          | Covered with solder more than 95% of the dipped portion of the terminal. |

| 13  | Sensor Body Strength | R0.5 pressure jig, 10N, $10 \pm 1$ sec hold | 無          | 1 time     | 22[10%]          | Mechanical<br>Characteristics                                            |

#### [ 前処理条件 ](Ref.: EIAJ ED4701-2 B101A)

1) 飽和加湿処理

(Ta= +85°C, RH= 30%, t= 168 hours, + Ta= +30°C, RH= 70%, t= 168 hours)

- 2) 赤外線リフロー (continuously for 3 times)

- 3) 水蒸気エージング (4 時間)

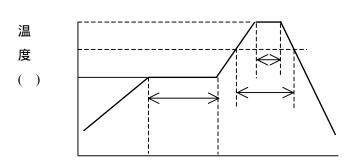

時間(秒) 図.赤外線リフロー条件

### [18] 半田付けリフロー条件

半田付けリフロー条件を以下に示します。

予備加熱:(+150~+190 ) × (90±30秒) +220 帯域:20~50秒

本加熱: +235~+250 ピーク

(10 秒以内)

加熱雰囲気:大気もしくは N2

図2. 半田付けリフロー条件

尚、リペア条件については、+250~+270 ×30秒以内 加熱時間+150秒以内(予備加熱70秒含む)で実施してください。但し、吸湿した製品を使用する場合は、必ずベーキングした後にリペアを実施してください。

#### [19] 注意事項

- 1) この製品は C-MOS IC を使っております。過度な静電気を印加しないようにしてください。

- 2) 安定した動作を保持するために AVDD-GND 端子間に  $0.47\mu F$  以上の X5R セラミックコンデン サを、DVDD-GND 端子間に  $0.01\mu F$  以上の X5R セラミックコンデンサを実装してお使いください。これらのコンデンサは端子近傍に設置してください。

- AVDD と GND の配線は高周波でのインピーダンスを減らすように太くしてください。

- 4) 保管方法 (防湿梱包状態)

高温多湿、直射日光の当たる場所、温度変化の激しい場所、塵埃の多い場所および 腐食性ガスの環境には放置しないで下さい。

保管時の温湿度は、+5 ~+30 、70%RH以下を保持し、1年以内にご使用下さい。 (尚、保管期間を超えた製品については、本仕様を満足しない場合もございます)

- 5) 防湿梱包開封後の使用条件

- +5 ~+30 、70%RH以下の環境で保管する場合は、7日以内にご使用下さいただし、防湿庫 (+5 ~+30 、30%RH以下)内での保管を推奨します。

- +30 、10%RH以下の防湿庫内で保管する場合は、1年以内にご使用下さい。 上記 の条件で、開封後7日を超える場合は、下記の条件でベーキングを実施し、 ご使用下さい。

<ベーキング条件>

- (ア) テーピング状態では、+60 ×168Hr または+40 ×200Hr

- (イ) 耐熱トレー状態では、+125 × 24Hr

- (ウ) ベーキング回数は2回までとして下さい

ただし、初回開封後は使い切りを推奨します。

- 6) 2本の GND 端子は、厚く短い配線で短絡させてください。

- 7) 本製品の OTP メモリ部のデータは、書き換えできません。

- 8) 安定した動作を保持するために AVDD-GND 端子間に  $0.47\mu F$  以上のセラミックコンデンサを、 DVDD-GND 端子間に  $0.1\mu F$  以上のセラミックコンデンサを実装してお使いください。

- 9) センサ特性は、実装基板および実装時の熱の影響により変化することがあります。実装後には、磁気センサの感度と原点を校正することを推奨します。

- 10) 本製品は、強磁性体のような磁気の乱れを起こす部位には搭載しないでください。